カスタム電源開発・設計 豆知識

2023.02.15

スイッチング素子の選定方法

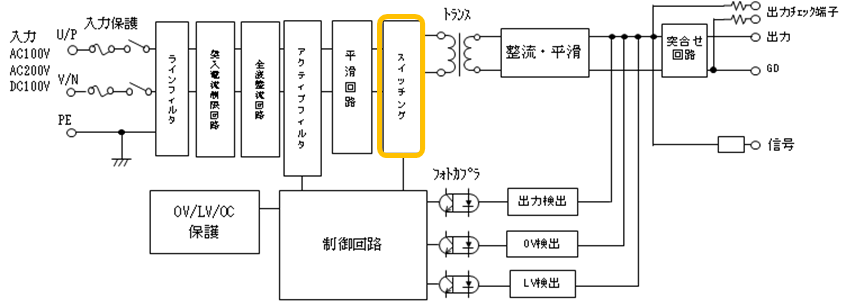

スイッチング電源の元となるスイッチング素子にはパワートランジスタ・MOS FET・IGBT等があり、それぞれに特徴があるため、仕様に合せて選定する必要があります。

まず、各々のスイッチング素子の特徴としては、下記が挙げられます。

| 品種 | 応答速度 | 駆動電力 | 電流容量 |

| パワートランジスタ | 遅い | 大 | 少 |

| MOSFET | 速い | 少 | 大 |

| IGBT | 遅い | 少 | 大 |

一般的に500Wクラス以下の電源では、MOS FETが主流で使用されています。そこで今回は、MOS FETの選定方法や設計上で注意すべき注意ポイントについて、下記に示します。

1.MOSFET選定時の注意ポイント

選定にあたっては、部品の仕様を満足し、且つ決められた項目に対して部品余裕度を満足することは絶対条件ですので、まずは主要な仕様項目について検討していきます。

| 項目 | 説明 |

| ドレイン-ソース間

耐圧VDSS |

MOSFET は耐圧が高いほどオン抵抗が高くなる傾向があることから,安易に高耐圧品を選定しない事。安易に高耐圧品を選定した結果、損失を増やしては意味がない。 |

| スレッシュホールド電圧

Vth |

VGSの値によって流し得る電流が制限されるため注意が必要。

また、VGSが低いほどオン抵抗が大きくなる傾向があることに注意すること。 |

| スイッチング速度 | 素子のトータル損失にスイッチング損失が大きく影響する為、ハイスピードの素子を選択する必要があるが、スイッチング速度とオン抵抗は一般にトレードオフの関係があり,高速になるほどオン抵抗が高くなるので、注意が必要。 |

| 入力容量

帰還容量 帰還容量 |

入力容量はドライブ側の出力抵抗と組み合わさって時定数を形成する為、入力容量が小さいものを選ぶ必要がある。また、帰還容量crssが急峻でないものを選定すること。駆動電圧10V付近の容量変化⊿Crss/⊿VDSが少ないものが好ましい。 |

2.設計時の注意事項

VDSSなどの主要スペックの他にも、選定にあたっては詳細スペックも合わせて確認することが重要となりますが、ポイントとしては下記が挙げられます。

①開発する機器に本当に必要な特性に着目して、優先すべき特性を見極めて選定する。

②部品選定時、最大定格,電気的特性比較だけの比較で終わらせないこと。

Crss,ASOなど特性グラフの比較をすると共に、周辺定数(ゲート抵抗)の定数最適値も設計する。

③並列接続時の電流バランスを考慮すること。

パターン設計時、電流バランスのバラツキを最小にする為、モード幅,長さのバランスを図ること。

3.メーカーカタログの各項目に対する留意点

またカタログにはスペックのみが記載されていることが多いので、ここではスイッチング電源を設計する際の留意点を記載致します。詳細検討の参考にしてください。

| 項目 | 記号 | 温度の影響 | 留意点 |

| ドレイン・ソース破壊電圧 | V(BR)DSS | 有 | オン抵抗との相関あり |

| ドレイン遮断電流 | IDSS | 有 | 温度依存性が大きいが損失的には小さい |

| ゲート遮断電流 | IGSS | 無 | 保護ダイオード内蔵品は,数十nA~数μA |

| ゲート・ソース遮断電圧 | VGS(off) | 有 | スイッチング動作時のノイズや

スイッチング時間tr,tfに影響 |

| ドレイン・ソースオン抵抗 | RDS(on) | 有 | オン損失を決めるもっとも重要なパラメータ。

温度と共に上昇することに注意。 |

| 入力容量 | Ciss | 無 | VDS依存性あり。アナログ動作時のドライブ損失指標 |

| 出力容量 | Coss | 無 | VDS依存性あり。軽負荷時の下降時間tfに影響 |

| 逆伝達容量 | Crss | 無 | VDS依存性あり。スイッチング時間tr,tfを左右する。 |

| トータルゲートチャージ量 | Qg | 無 | ドライブ損失を決める特性。

ゲート駆動電圧に大きく依存。 |

| ゲート・ドレインチャージ量

(ミラー容量) |

Qgd | 無 | スイッチング時間tr,tfを決める特性。

電源電圧VDDに依存 (VDDが上昇すると大きくなる) |

| ターンオン遅延時間 | td(on) | 無 | Rg,Qgdやゲート駆動電圧により決まる。

インバータ用途のターンON損失を左右する。 |

| 上昇時間 | tr | 無 | |

| ターンオフ遅延時間 | td(off) | 無 | Rg,QgdやVthにより決まる。

スイッチングOFF時のサージ電圧(ノイズ)を左右する。 |

| 下降時間 | tf | 無 | |

| ダイオード順電圧 | VDF | 有 | VGSに正バイアス印加するとオン抵抗と同特性になる。 |

| ダイオード逆回復時間 | trr | 有 | 短絡電流、ノイズを抑えるためにはdi/dtを下げる。 |

ここからは、No.1~3の注意点や留意点を踏まえて、スイッチング素子(MOS FET)

を実例に合せて選定して参ります。

<顧客要求仕様>

(1)入力電圧:DC400V(MOS FETに掛かる電圧)

(2)出力仕様:5V,10A

<部品の選定>

MOS FETのスイッチング電流とVDSの計算式を以下に示す。

IDp=Io×N2/N1+⊿I/2

VDS=Vi/(1-D)

定格出力電流のときのスイッチング電流とVDSを上記式より求める。

IDp=10A×5ターン/100ターン+1A/2=1A

VDS=400V/(1-0.4)=666V

VDS=666Vtyp,部品余裕度80%より

VDS定格>666/0.8=833V

VDS=833V以上でId=1A以上のMOS FETを選定する必要がある。

上記必要特性より、東芝製MOS FET 2SK4115を選定します。2SK4115の電気的特性は下表となります。

| 項目 | 記号 | 定格 | 単位 |

| ドレイン・ソース間電圧 | VDSS | 900 | V |

| ドレイン電流 | ID | 7 | A |

| ドレイン・ソース間オン抵抗 | RDS(ON) | 1.6(typ) | Ω |

| チャネル・外気間熱抵抗 | Rth(ch-a) | 50 | ℃/W |

| チャネル・ケース間熱抵抗 | Rth(ch-c) | 0.833 | ℃/W |

なお、スイッチング素子は大きく発熱をするので、電気的特性のほか損失もしっかり確認しておくことが必要となります。

<損失の計算>

今回の事例でいうと、FETの損失は以下の合計となる。

ターンオン損失 P1=ID×VDS×tr/(6×T)=1A×400V×0.1us/(6×5us)=1.3W

オン損失 P2=ID2×Ron×Ton/T=1A2×1.6Ω×2us/5us=0.64W

ターンオフ損失 P3=ID×VDS×tf/(6×T)=1A×666V×0.1us/(6×5us)=2.2W

P=P1+P2+P3=1.3W+0.64W+2.2W=4.14W

上記よりこのMOS FETの損失は4.14Wとなり、ヒートシンク・放熱板なしで使用を考えた場合の温度上昇は

4.14W×50℃/W=207℃ となります。

よって、半導体のチャネル温度150℃を大きく超えることからヒートシンク・放熱板が必要となります。

「スイッチング電源の回路構成と設計方法」ハンドブック無料プレゼント

産業用カスタム電源 開発・設計 Naviを運営するアイガ電子工業株式会社では、電源回路設計・スイッチング電源設計を行うエンジニアの方々に向けWEBサイト上で有益な情報を発信しておりますが、「スイッチング電源の回路構成と設計方法」ハンドブックを刊行し、ご希望される方には無料プレゼントを行っています。少しでもご興味をお持ちの方は、下記リンクよりご確認ください。

関連する豆知識一覧

-

電源設計の基礎

2026.02.19

産業用電源の「定電流制御」精度を高める回路設計のポイント

一般的な産業用電源は、電圧を一定に保つ「定電圧制御」が主流です。しかし、メッキ処理、レーザー加工、あるいはEV向け二次電池の検査装置など、機…

-

電源設計の基礎

2026.01.16

電子機器や産業機器の設計・製造にまつわる当社のトータルソリューション

電子機器や産業機器の設計を進める中で、 「当初は一部の要素だけの検討だったが、話を進めるうちに他の課題も見えてきた」 そのような…

-

電源設計の基礎

2025.12.15

カスタム電源で納期短縮を実現するための5つのポイント

弊社へ寄せられるご相談の中で最近増えているのが「早く製品を納めてほしい」という、短納期に関するご要望です。しかし、カスタム電源の開発は通常、…

-

電源設計の基礎

2025.10.27

スイッチング電源とドロッパー電源の採用判断基準

ドロッパー電源はノイズ特性に優れますが、昨今はスイッチング電源も低ノイズ化しており、産業用カスタム電源は、現在スイッチング電源が主流となって…

-

電源設計の基礎

2025.09.25

高速スイッチング化に伴う カスタム電源のノイズ対策

電源設計に携わる方ならご存じかと思いますが、電源のスイッチング周波数を高めることで、トランスやコンデンサなどの受動部品を小型化でき、装置全体…

-

電源設計の基礎

2025.08.21

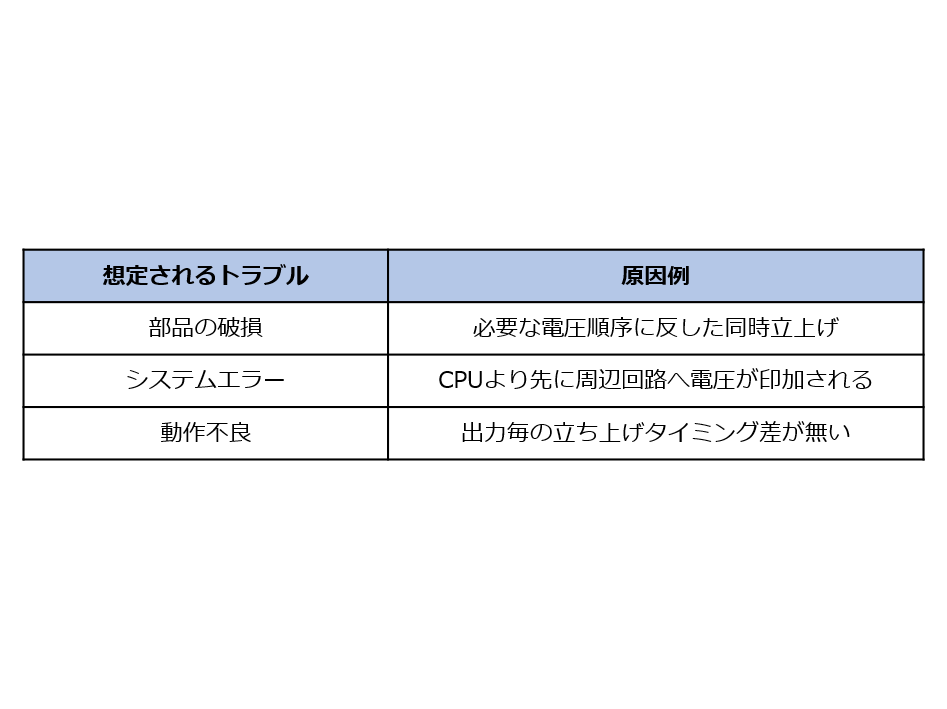

多チャンネル電源を安全に立ち上げるための設計ポイント

産業機器の電源を多チャンネル化することで、CPU用、通信回路用、モーター制御用など複数の電圧を一台の電源装置から供給することでき、装置全体の…